# **Formalising Chisel**

#### Kenneth J. Turner

Department of Computing Science and Mathematics University of Stirling, Stirling FK9 4LA, Scotland

*Telephone:* +44-1786-467-420 *Facsimile:* +44-1786-464-551 *Email:* kjt@cs.stir.ac.uk *Web:* http://www.cs.stir.ac.uk/~kjt/

7th September 1999

### Introduction

- Chisel:

- graphical notation for describing services/features

- developed at BellCore

- formalisation desirable:

- tighten up rules and interpretation

- Lotos and SDL considered

- mapping to SDL developed

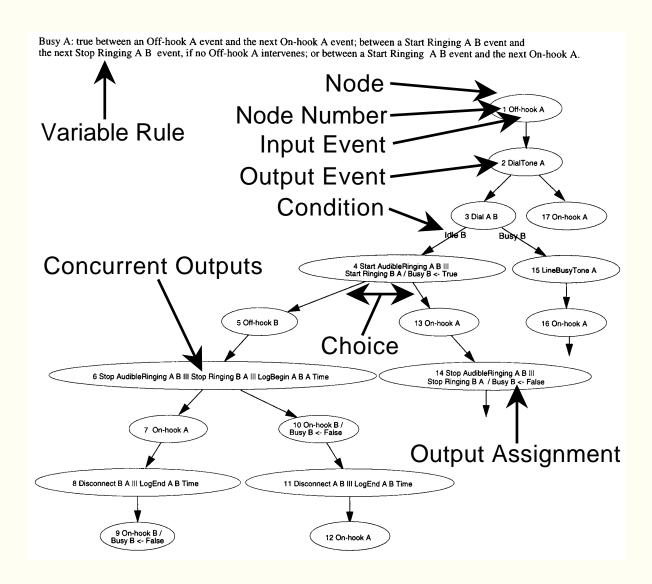

## Sample Chisel Diagram

### POTS base-line in Chisel:

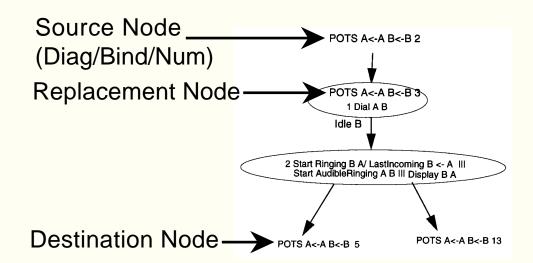

## Sample Feature Diagram

Calling Number Delivery in Chisel:

### **Need for Formalisation**

- rules for constructing diagrams loose

- rules for incorporating features loose

- better handling of concurrency needed

- rigorous interpretation would offer:

- simulation

- validation and verification

- model-checking

- test derivation

- already some formalisation: FSM, RE, MSC, process algebra

### **LOTOS and SDL for Chisel**

- Lotos mapping apparently used by Ottawa, though not made explicit

- SDL mapping apparently not developed

| Aspect          | Lotos         | SDL              |

|-----------------|---------------|------------------|

| semantics       | fully defined | clear?           |

| complexity/size | medium        | high             |

| analysis        | good          | validation       |

| communication   | synchronous   | asynchronous     |

| input-output    | neutral       | directed         |

| globals         | no (faked?)   | yes (no mutex)   |

| concurrency     | yes           | yes              |

| redefinition    | no            | yes (but limits) |

## **Chisel Diagram Rules**

- each event designated input/output according to event names

- node is input/output/interleaved output

- alternating input/output nodes (not entirely necessary)

- source diagram node assumed input (not entirely necessary)

- replacement diagram node:

- must be input node

- must have same event as original

- binding identical to source node

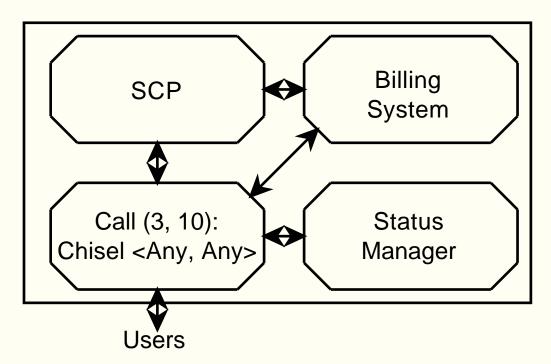

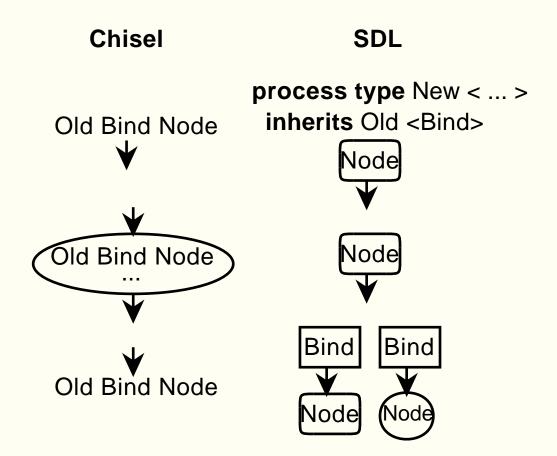

## **Approach using SDL**

SDL structure for a Chisel 'network':

- Chisel diagram separate process type

- features rigorously combined with each other and POTS

- complete description processed by tools:

- standard problems (deadlock, unspecified reception, ...)

- POTS+Feature as MSC against POTS+Feature1+Feature2

- automated test derivation

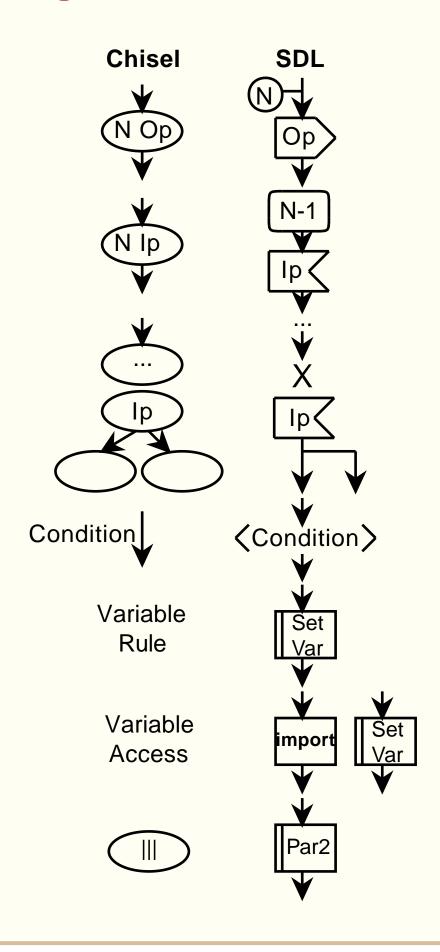

# **Chisel Diagram in SDL**

## **Feature Diagram in SDL**

### Conclusion

- formalisation of benefit to Chisel

- LOTOS vs. SDL considered, but SDL worked through

- mapping rules developed in outline

- future work:

- small changes to existing diagrams

- translation to SDL manual/automatic

- trying various forms of validation

- application to FIW'98 competition